## Co-integration of Ge detectors and Si modulators in an advanced Si photonics platform

Peter Verheyen<sup>a</sup>, Guy Lepage<sup>a</sup>, Joris Van Campenhout<sup>a</sup>, Marianna Pantouvaki<sup>a</sup>, Philippe Absil<sup>a</sup>, Peter De Heyn<sup>b</sup>, Wim Bogaerts<sup>b</sup>, Pieter Dumon<sup>b</sup>, Shankar Selvaraja<sup>b</sup>.

aimec, Kapeldreef 75,3001 Leuven, Belgium

<sup>b</sup>Photonics Research Group, Dept. of Information Technology, Ghent University – imec, St.-Pietersnieuwstraat 41,9000 Ghent, Belgium

Keywords: modulator, Ge detector, Si photonics platform

#### **ABSTRACT**

A Si photonics platform is described, co-integrating advanced passive components with Si modulators and Ge detectors. This platform is developed on a 200mm CMOS toolset, compatible with a 130nm CMOS baseline. The paper describes the process flow, and describes the performance of selected electro-optical devices to demonstrate the viability of the flow.

#### INTRODUCTION

In the last few years, silicon photonics has become the focus of attention as an enabler for low-cost, high-bandwidth optical interconnects. The integration of optical components on silicon allows for the use of a large volume of manufacturing capability, and it can allow for tight integration of the logic components with the optical interconnect layer. A full optical platform needs, apart from passive components, active components enabling the conversion from the optical to the electrical domain and vice versa. This paper describes such a Si photonics platform, combining advanced passive capability using four-level Si patterning, with silicon electro-optic modulator and germanium waveguide photo-detector modules.

#### PROCESS OVERVIEW

#### Advanced passives baseline process

The starting substrates used for this optical platform flow are commercially available 200mm SOI wafers, with a Si thickness of 220nm on top of a buried oxide thickness of  $2\mu m$ . On top of the SOI an additional oxide/poly-silicon stack is deposited, which allows for additional degrees of freedom in the design of optical components.

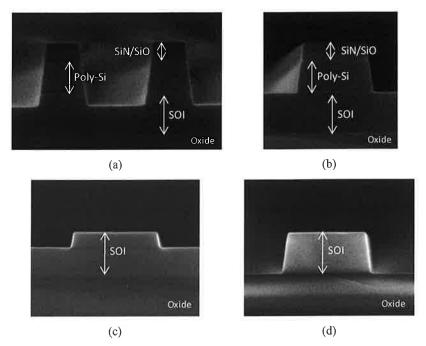

The full layer-stack is patterned using four levels, all defined in 193nm lithography, and patterned using dry etching. The first two levels pattern the poly-Silicon/Oxide stack. The first sequence etches the full poly-Si and oxide layer, and removes also 70nm of the underlying Si, as indicated in XSEM in Figure 1 (a). In this level, low loss couplers can be defined [1], as well as compact MOS ring modulators [2]. In the second sequence, the poly-silicon layer is etched, stopping on the oxide underneath. (Figure 1(b)). In this level, poly-Si waveguides can be designed, as well as polarization rotators [3]. The next two levels pattern the remaining 220nm Si: the first one removes 70nm of the top Si layer (Figure 1c). This level is used for shallowly etched (low loss) waveguides [4], as well as crossings [5], and waveguide apertures for arrayed waveguide gratings [6]. The final level patterns the full 220nm Si, stopping in the bottom oxide layer (Figure 1d). Here the fully etched Si waveguides are defined, and it allows for the design of compact ring devices[7], and bends with radii<5μm.

The advanced passives baseline flow finishes with a planarization module. In order to obtain a good gap-fill, a high density plasma oxide deposition is used. This oxide is planarized using chemical-mechanical polishing (CMP). In order to obtain a controlled planarization, the poly-Si layer is patterned with an oxide/SiN hard-mask on top. The slurry used during polishing has a high selectivity towards this top SiN layer, so it acts as a stopping layer. After the polishing sequence, the SiN layer is selectively removed using a wet etch in hot phosphoric acid.

Figure 1: SEM crossections at the different stages of the patterning of the advanced passives stack: (a) After Raise Fiber Coupler etch. (b) After Fiber coupler window etch, (c) after FC etch, and (d) After WG etch.

#### Si Modulator and Ge detector Modules.

For the modulators, we introduce dopants in three locations in the process flow. A first set of implantations are done before the oxide/poly stack deposition. These are relatively low dose Boron and Phosphorous implantations, yielding dopant concentrations in the  $10^{18}$  cm<sup>-3</sup> range, providing the p-type and n-type regions for the modulators, and the channel doping for the accumulation modulators. The second set of implants are done after the advanced passives patterning, providing higher dose B and P implants in Silicon ( $10^{20}$ cm<sup>-3</sup> range), which provides a good ohmic contact. Finally the poly-silicon is implanted after the full planarization module. This creates the gate doping for the accumulation modulators. These junctions are spike-annealed at  $1075^{\circ}$ C.

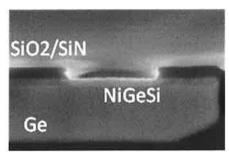

After the final junction anneal (which is the highest point in the thermal budget of the process flow), we enter the Ge detector modules. After a hard-mask deposition, trenches are etched on top of the poly-Si. This poly-Si is subsequently removed very selectively towards the oxide, after which a slight recess of the SOI layer is done. At this point Germanium is selectively deposited inside the trenches. A high degree of Ge relaxation at low defect density is obtained by growing thick layers (typically  $2\mu m$ ), and using a post deposition thermal anneal at  $850^{\circ}C$  [9]. During this thermal process, threading dislocations move through the Ge and terminate at the Ge/Oxide interfaces. This way, the impact of these dislocations on the dark current of the detector can be reduced. This thick Ge layer is subsequently planarized by CMP, selective towards the oxide, yielding a flat Ge surface. Figure 2 below shows the Ge layer after final planarization.

The Germanium is also implanted with phosphorous and boron, to create both horizontal and vertical pin diodes. The junction anneal of the Ge is performed at  $550^{\circ}$ C.

For contacting the Ge regions, two options are considered. In the first option, the germanium is protected during the Ni silicidation reaction. A typical sheet resistance of 9 Ohm/square is obtained for the silicide. In this case, contacts to the silicon regions land on the silicide, while the Ge regions are contacted directly on top of the germanium. In the second option, a local and simultaneous Ni silicidation and germanidation is used. In order to improve the process window overlap for the simultaneous reaction of Ni with Si and Ge, a selectively grown epitaxial Si<sub>1-x</sub>Ge<sub>x</sub> layer is deposited after the Ge CMP (and before the implantations). The addition of Si in the Ge regions brings the process window for the Ni-

germanidation reaction closer to the Ni-silicidation reaction. Figure 2 shows a XSEM picture of a locally formed germanide.

Figure 2: XSEM image of a local silico-germanide.

#### Metallization.

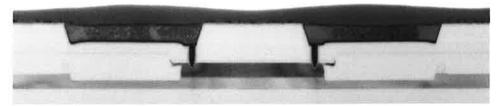

The pre-metal dielectric (PMD) stack is deposited using low temperature, high density plasma CVD deposition, and planarized using CMP down to 400nm on top of the Ge. The thickness of this PMD stack determines the proximity of the top metallization to the optical structures, and is therefore to be considered an important factor. In this PMD layer trench contacts are formed, with a width of 0.15 µm. These trenches are filled with W, which is polished down to the PMD oxide. For the metallization layer a Cu damascene process is used. The results obtained in this work are obtained contacting directly on top of the Cu bondpads. Figure 3 below shows a XTEM image of a horizontal p-i-n Ge detector after full metallization.

Figure 3: Cross section picture of a horizontal Ge diode, after Cu metallization.

#### CHARACTERIZATION OF MODULATORS AND DETECTORS

### Advanced Passives Performance.

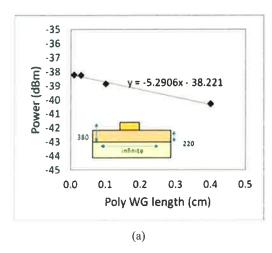

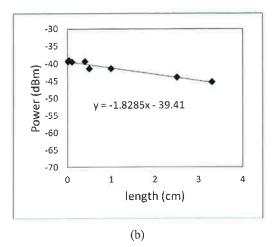

In Figure 4 the loss of SOI waveguides and hybrid poly Si/Si waveguides as a function of waveguide length are shown. These numbers are obtained after Cu metallization as described in the previous section. After full processing, an average waveguide loss of 1.8dB/cm is demonstrated for Si waveguides with a width of 400nm. The hybrid poly-Si/Si waveguides have an average WG loss of 5.3dB/cm for a dimension of 350nm.

Figure 4: Transmitted power as a function of WG length for (a) 350nm wide hybrid poly Si/Si WG showing 5.3dB/cm loss, and (b) 400nm wide Si WG, with an average of 1.85dB/cm loss.

#### Ring modulators

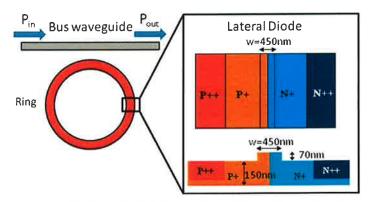

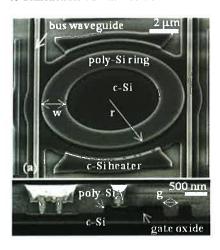

Figure 5 shows a schematic view of the depletion type ring modulators that have been realized in this photonics platform [8], albeit without the Ge detector co-integrated. The structure discussed below have a waveguide width of 450nm, and the spacing between the ring and the bus waveguide is 570nm. Ring diameter for the structures under analysis in this work is  $40\mu m$ . The typical doping concentration in the n and p doped region are around  $10^{18}$  cm<sup>-3</sup>.

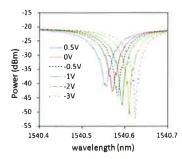

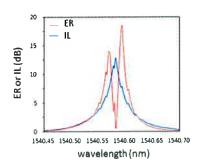

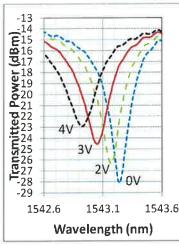

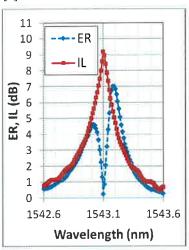

Figure 6a shows the transmission spectrum of the ring as a function of applied bias over the p-n junction, indicating the shift of the drop wavelength as a function of bias condition. Based on this static performance characteristic, the extinction ratio and the insertion loss can be calculated, as shown in Figure 6. The structure under study shows a maximum extinction ratio of 18.5 dB at an insertion loss of 7.9 dB at  $1 V_{p-p}$ .

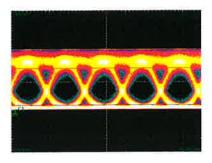

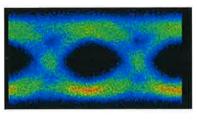

High speed measurements were performed on these devices: the eye diagram depicted in Figure 6 demonstrates 10Gb/s performance at 1.2V peak-peak. More details regarding performance of this structure can be found in [8].

Figure 5: schematic view of the depletion type ring modulators discussed in this paper.

Figure 6: Carrier depletion type ring modulator (a) Through-port transmission as a function of bias voltage. (b) Extinction ratio and insertion loss as a function of wavelength. (c) Open eye diagram demonstrating 10Gb/s for 1.2V<sub>p-p</sub>.

Accumulation MOS based modulators also have been demonstrated using the platform, including co-integration with the Ge photo-detector modules. Figure 7 below shows a top-down and cross-section SEM picture of such a structure. By applying a bias voltage in accumulation over the MOS capacitor, the carrier density is modulated, changing the phase difference over the ring modulator, thereby shifting the resonance frequency. Similar to the depletion modulators of the previous section, the static performance can be measured as shown in Figure 7 below. Using this structure, we are able to demonstrate 7dB at insertion loss of 5dB for these devices, for 1Vpp drive signal [2].

Figure 7: (a) TDSEM and XSEM of a carrier accumulation type modulator. (b) Transmitted power as a function of wavelength, and applied gate voltage. (c) Extinction ratio and insertion loss as a function of wavelength for 1V peak to peak.

The dynamic performance of this structure is limited at 3Gb/s, because of the large parasitic capacitance and resistance, but device design and implantation optimization is expected to significantly improve this.

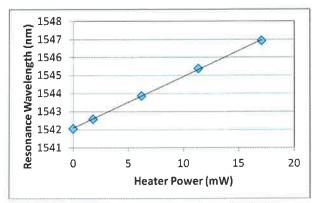

Figure 8: Resonant wavelength shift of a MOS ring device as a function of applied heater power.

#### **Integrated Si heaters**

The platform flow allows for the introduction of resistive heaters close the ring modulators. The resistive heaters are realized using the highly doped P implants. Figure 7 shows the integrated Si heaters available next to the modulator ring. The impact of the heater element on the resonance wavelength of a MOS ring device is shown in Figure 8: the resonance wavelength shifts by 0.29nm/mW.

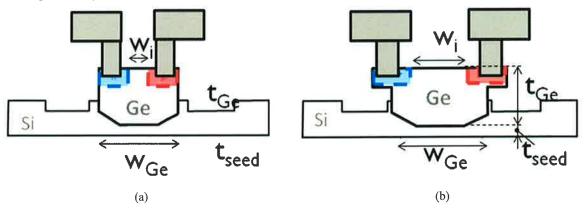

Figure 9: Schematic crossection a horizontal PIN Ge detector (a), and a 'ribbed' structure (b), bringing the contact regions further away.

#### Ge-on-Si waveguide photo-detectors

The Ge detectors studied in this work are lateral p-i-n structures. Figure 9 shows a schematic cross-section of two types of the device considered: standard structures, and 'inverted rib' structures. For the standard structures, the oxide opening is chosen to be the same size as the underlying poly-Si. By opening up an oxide window larger than the original underlying poly line, and by carefully tuning the oxide etch, the Ge lateral overgrowth and the CMP process, it is possible to create the 'inverted rib' structures as shown in Figure 9b. In this case, the contacts to the doped regions can land further away from the optically active region of the detector.

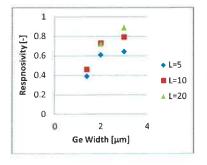

In both designs, important parameters are the intrinsic region width  $(w_i)$ , the Ge thickness  $(t_{Ge})$ , Ge width  $(w_{Ge})$ , and the Si seed thickness  $(t_{seed})$ . Figure 11 shows the impact of the length and the Ge width of the structure on the responsivity of the detector. It clearly shows that the responsivity decreases as a function of width, due to the proximity of the metallic contacts, and the associated loss. Increasing the length of the device, increases the responsivity, but this impact saturates beyond 20 $\mu$ m. For the standard photo-detector structure, a responsivity of 0.72A/W was measured at 1.5 $\mu$ m

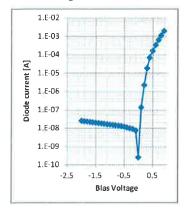

wavelength for a  $2\mu m$ -wide device. This increased up to 0.9A/W for a  $3\mu m$ -wide device. Inverted rib detectors have been measured with a responsivity of 0.9A/W for a Ge width down to  $1.4\mu m$ . Figure 10 shows a dark current characteristic for a photodiode, showing that leakage currents down to 100nA can be obtained.

High speed characterization was able to demonstrate open eye diagrams at 10Gb/s at a -2V bias for  $5\text{x}2\mu\text{m}^2$  structures, as shown in Figure 12.

Figure 10: Leakage current under dark and light conditions, for different device lengths as a function of voltage. (L=50μm, W=3μm)

Figure 11: Impact of the Ge width design parameter on the responsivity, showing the detrimental impact of the closer proximity of the metal contacts

Figure 12: Open eye diagram at 10Gb/s at a -2V bias condition.

#### **CONCLUSIONS**

A Si photonics platform is described, co-integrating advanced passive components with Si modulators and Ge detectors. This platform is developed on a 200mm CMOS compatible toolset, as used by a 130nm CMOS baseline.

### REFERENCES

- [1] Vermeulen, D., Selvaraja, S., Verheyen, P., Lepage, G., Bogaerts, W., Absil, P., Van Thourhout, D., Roelkens, G., "high-efficiency fiber-to-chip grating couplers realized using an advanced CMOS-compatible silicon-on-insulator platform", Optics Express, 18(17), p.18278-18283 (2010)

- [2] Van Campenhout, J. et al, "Low-Voltage, Low-Loss, Multi-Gb/s Silicon Micro-Ring Modulator based on a MOS Capacitor", Optical Fiber Communication Conference, OSA Technical Digest (CD) (Optical Society of America, 2012), paper OM2E.4.

- [3] Vermeulen, D., Selvaraja, S., Verheyen, P., Absil, P, Bogaerts, W., Van Thourhout, D., Roelkens, G., "Silicon-on-Insulator polarization rotator based on a symmetry breaking silicon overla"y, accepted for publication in Photonics Technology Letters, (to be published).

- [4] Bogaerts, W., Selvaraja, S., "Compact Single-mode Silicon Hybrid Rib/Strip Waveguide with Adiabatic Bends,", IEEE Photonics Journal, 3(3), p.422-232 (2011)

- [5] Bogaerts W., Dumon, P., Van Thourhout, D., Baets, R., "Low-Loss, Low-Crosstalk Crossings for SOI Nanophotonic Waveguides", Optics Letters, 32(19), p.2801-2803 (2007)

- [6] Bogaerts, W., Dumon, P., Van Thourhout, D., Taillaert, D., Jaenen, P.,, Wouters J., Beckx, S., Baets, R., "Compact Wavelength-Selective Functions in Silicon-on-Insulator Photonic Wires", J. Selected Topics in Quantum Electronics, 12(6), p.1394-1401 (2006)

- [7] Bogaerts , W., De Heyn, P. , Van Vaerenbergh, T. , De Vos, K., Selvaraja, S., Claes, T., Dumon, P., Bienstman, P., Van Thourhout, D., Baets, R., "Silicon Microring Resonators", Lasers and Photonics Review (invited), (2011)

- [8] Pantouvaki, M. , et al, "Lateral versus Interdigitated Diode Design for 10~Gb/s Low-Voltage Low-Loss Silicon Ring Modulators," in IEEE Photonics Society Optical Interconnects Conference (IEEE, 2012), to be presented..

- [9] Loo, R. et al, "High Quality Ge Virtual Substrates on Si Wafers with Standard STI Patterning", Journal of The Electrochemical Society, 157, H13-H21, 2010.

# 2012 Photonics Europe

16-19 April 2012

Technical Programme spie.org/pe

#### Location

Square Brussels Meeting Centre Brussels, Belgium

#### Conference dates

16-19 April 2012

#### Exhibition dates

16-18 April 2012

#### Technologies

- Micro/Nano Technologies

- Disruptive Organic and Biophotonics

- Highly Integrated and Functional Photonic Components

- Advances in Laser and Amplifier Technologies

- Photonics in Industrial Applications

#### **SESSION 5** Wednesday 18 April Room: 216 ...... Tues. 11.00 to 12.40 **SESSION 7** Silicon and Germanium Modulator Session Chair: Goran Z. Mashanovich. Silicon Modulators Univ. of Surrey (United Kingdom) Session Chair: Laurent Fulbert, CEA-LETI (France) 11.00: Ring resonator silicon optical modulator based on interleaved pn junctions, Melissa Ziebell, Delphine Marris-Morini, Gilles Rasigade, Institut d'Électronique Fondamentale (France); Jean-Marc Fedeli, CEA-LETI-Minatec (France); Eric Cassan, Laurent Vivien, Institut d'Électronique Fondamentale 08.30: A study of variations in the free carrier absorption eect as a function of CMOS technological node, Alexander Serb, Timothy G. Constandinou, Konstantin Nikolic, Imperial College London (United Kingdom).....[8431-28] 08.50: CMOS-compatible electro-optical Mach-Zehnder modulator based 11.20: Slow light-enhanced carrier depletion modulators with 1V drive voltage, Antoine Brimont, Univ. Politécnica de Valencia (Spain); Dave Thomson, on the amorphous silicon technology, Sandro Rao, Univ. Mediterranea di Reggio Calabria (Italy); Giuseppe Coppola, Mariano A. Gioffrè, Istituto per Frederic Gardes, Univ. of Surrey (United Kingdom); Jean-Marc Fédéli, CEA la Microelettronica e Microsistemi (Italy); Francesco G. Della Corte, Univ. Mediterranea di Reggio Calabria (Italy)......................[8431-29] 09.10: High-speed silicon optical modulator based on a pin diode, Melissa 11.40: Strain tuning of Ge electro-absorption modulators for Si photonics, Ziebell, Delphine Marris-Morini, Gilles Rasigade, Institut d'Électronique Fondamentale (France); Jean-Marc Fedeli, CEA-LETI-Minatec (France); Eric Ryo Kuroyanagi, Luan M. Nguyen, The Univ. of Tokyo (Japan); Tai Tsuchizawa, Nippon Telegraph and Telephone Corp. (Japan); Yasuhiko Ishikawa, The Univ. Cassan, Laurent Vivien, Institut d'Électronique Fondamentale (France). [8431-30] of Tokyo (Japan); Koji Yamada, Nippon Telegraph and Telephone Corp. (Japan); 09.30: Low-voltage high-speed Si Mach-Zehnder optical modulator with Kazumi Wada, The Univ. of Tokyo (Japan) . . . . . . . . . . . . . . . . . . [8431-20] multicascade p/n junctions along waveguides, Ryuichi Furutani, Hiroshima 12.00: The effects of strain on indirect absorption in Ge/SiGe quantum wells, Leon J. Lever, Zoran Ikonic, Robert W. Kelsall, Univ. of Leeds (United Kingdom); Maksym Myronov, David Leadley, The Univ. of Warwick (United Kingdom); Youfang Hu, Frederic Gardes, Nathan Owens, Graham T. Reed, Univ. of Surrey (United Kingdom).....[8431-21] **SESSION 8** 12,20: Electroabsorption based on quantum-confined Stark effect from Ge/SiGe multiple quantum wells, Papichaya Chaisakul, Delphine Marris-Morini, Institut d'Electronique Fondamentale (France); Giovanni Isella, Daniel Chrastina, Lab. for Epitaxial Nanostructures on Silicon and Spintronics (Italy); Mohamed Saïd Rouifed, Institut d'Électronique Fondamentale (France); Jacopo **Industry and Silicon Photonics** Session Chair: Lorenzo Pavesi, Univ. degli Studi di Trento (Italy) 10.30: Silicon photonics for optical interconnects in computing Frigerio, Lab. for Epitaxial Nanostructures on Silicon and Spintronics (Italy); Eleonora Gatti, Univ. degli Studi di Milano-Bicocca (Italy); Xavier Le Roux, applications (Invited Paper), Bert-Jan Offrein, IBM Zürich Research Lab. Samson Edmond, Eric Cassan, Jean-René Coudevylle, Laurent Vivien, Institut 11.00: Silicon photonics at ST (Invited Paper), Guido Chiaretti, 11.30: Opportunities and challenges of silicon photonics in optical networks (Invited Paper), Roberto Sabella, Ericsson Telecommunicazion (Italy) . [8431-34] **SESSION 6** Room: 216 . . . . . . Tues. 13.40 to 16.00 12.00: Silicon photonic, a technology for long haul WDM systems with high potential (Invited Paper), Gabriel Charlet, Alcatel-Lucent (France) . . . . [8431-35] **CMOS Photonics for Theranostics** Session Chair: Lorenzo Pavesi, Univ. degli Studi di Trento (Italy) 13.40: Real-time and low-cost biosensors based on photonic bandgap **SESSION 9** structures (Invited Paper), Jaime García-Rupérez, Javier G. Castelló, Veronica Toccafondo, Pere Perez-Millan, Univ. Politécnica de Valencia (Spain) : [8431-23] Silicon Photonics Integration 14.10: Silicon biosensors for point-of-care diagnostic (Invited Paper), Laura M. Lechuga, Ctr. d'Investigacions en Nanociència i Nanotecnologia Session Chair: Bert-Jan Offrein, IBM Zürich Research Lab. (Switzerland) 14,40: CMOS photonics for optical manipulation of particles and biosensing 13.30: Photonics-electronics Integration on CMOS (Invited Paper), Laurent (Invited Paper), Andrew W. Poon, Hong Cai, Ting Lei, Hong Kong Univ. of Science and Technology (Hong Kong, China) . . . . . . . . . . . . . [8431-25] 14.00: Si photonics toward WDM implementation on a chip (Invited Paper), 15.10: Pathogen detection system based on CMOS photonics (Invited Paper), Danxia Xu, Siegfried Janz, Adam Densmore, Pavel Cheben, Martin Vachon, Nicaulas Sabourin, Heather McIntosh, Heping Ding, Rubin Ma, André Delâge, Jens H. Schmid, Shurui Wang, William Sinclair, Jean Lapointe, Greg Lopinski, 14.30: Silicon as a platform for quantum photonics, Damien Bonneau, Erman Engin, Univ. of Bristol (United Kingdom); Kazuya Ohira, Nobuo Suzuki, Haruhiko Yoshida, Norio Iizuka, Mizunori Ezaki, Toshiba Corp. (Japan); Joshua Donling Zhang, Qing Yan Liu, National Research Council Canada W. Silverstone, Jianwei Wang, Univ. of Bristol (United Kingdom); Chandra M. Natarajan, Michael G. Tanner, Robert H. Hadfield, Heriot-Watt Univ. (United Kingdom); Sanders N. Dorenbos, Val Zwiller, Technische Univ. Delft (Netherlands); Jererny L. O'Brien, Mark G. Thompson, Univ. of Bristol (United Kingdom) 15.40: On-chip multiplexing concept for silicon photonic MZI biosensor array, Paul Muellner, Roman Bruck, AIT Austrian Institute of Technology GmbH (Austria); Matthias Baus, Matthias Karl, Thorsten Wahlbrink, AMO GmbH Kingdom)......[8431-78] (Germany); Rainer Hainberger, AIT Austrian Institute of Technology GmbH 14.50: Co-integration of Ge detectors and Si modulators in an advanced Si photonics platform, Peter Verheyen, Marianna Pantouvaki, Joris Van Campenhout, Guy Lepage, Philippe Absil, IMEC (Belgium); Hui Yu, Shankar K Selvaraja, Wim Bogaerts, Univ. Gent (Belgium) . . . . . . . . . . . . . . [8431-39] 15.10: New integration concept of PIN photodiodes in 0.35µm CMOS technologies, Ingrid Jonak-Auer, Jordi Teva, Jong Mun Park, Stefan Jessenig, Hot Topics II Tuesday 17 April, 16.30 to 18.30 hrs · Gold Hall Peter Kailbauer, Ewald Wachmann, austriamicrosystems AG (Austria) . [8431-40] For details, please see page 12